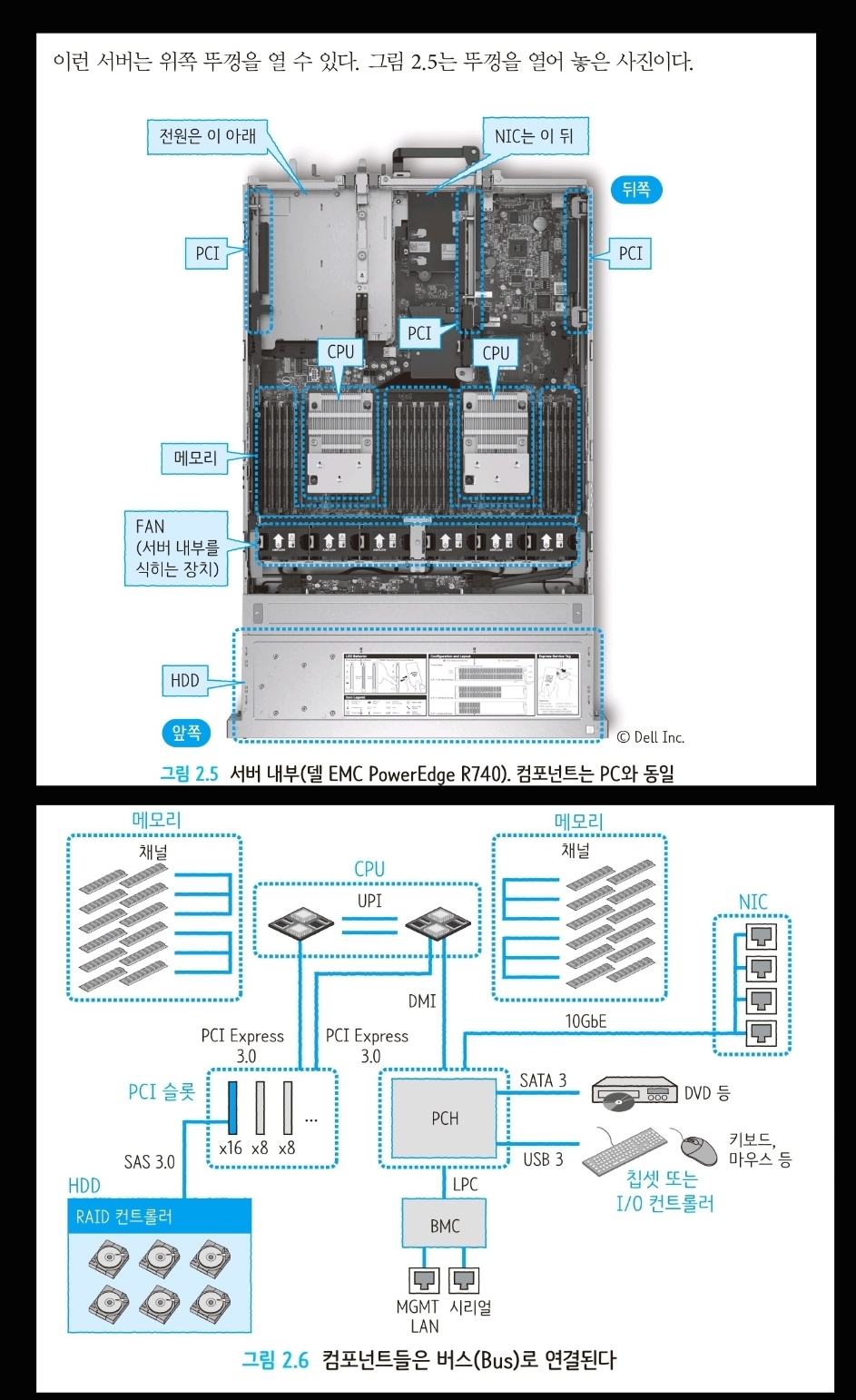

- 물리 서버 구조

- R740 분해 구성

- CPU가 두개로 구성 ⇒ 각 CPU와 메모리가 직접연결

- PCI Express : 외부 장치를 연결하는 곳으로, Xeon 아키텍쳐에선 CPU가 PCI를 직접 통제한다.

- BMC: 서버의 HW를 감시하는 독립 컴포넌트 , 해당 컴포넌트를 통해 서버상태확인(네트워크 혹은 직접)

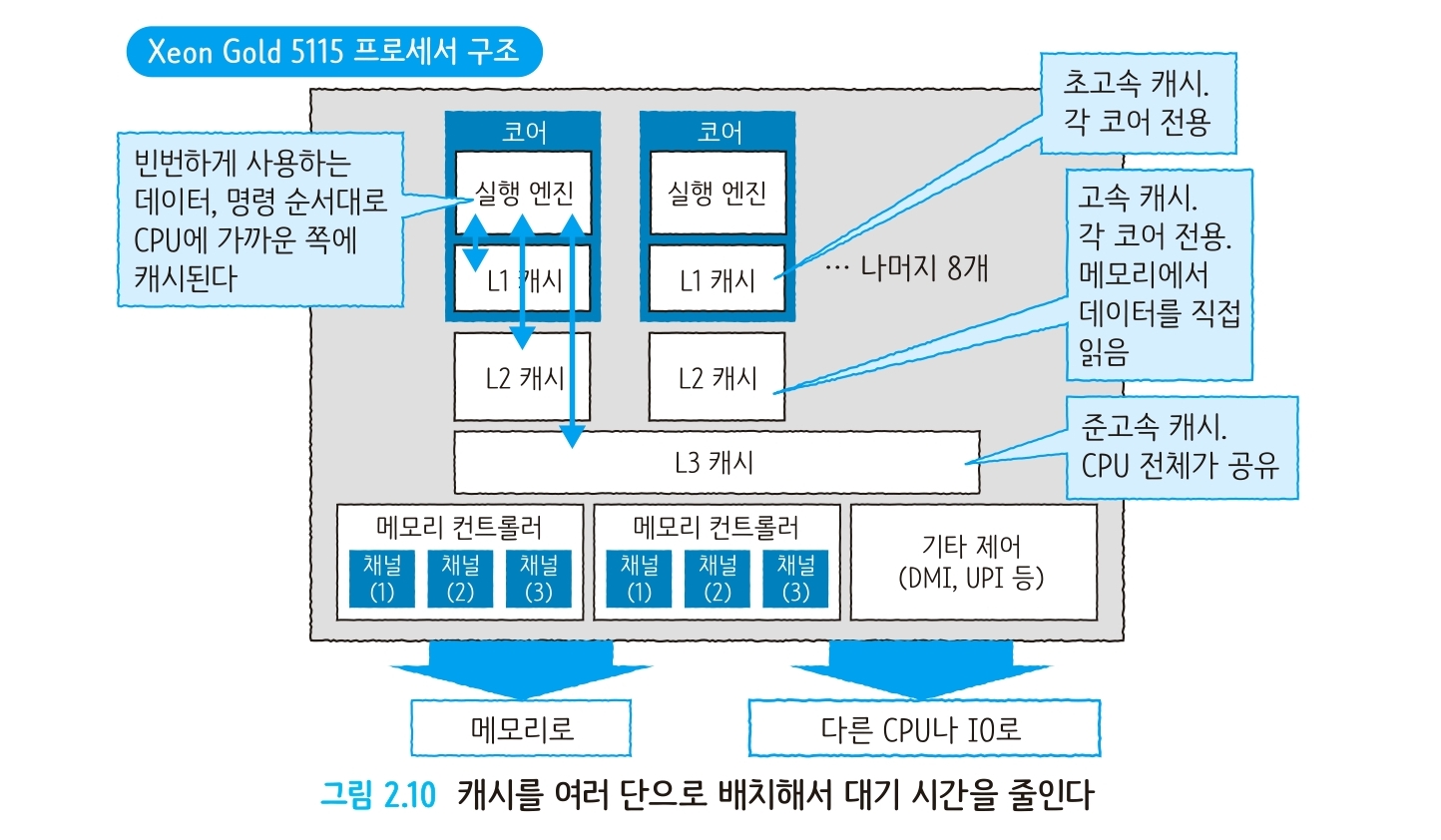

2. CPU 메모리 구조

- 메모리를 통해 CPU에선 필요한 메모리를 빠르게 접근

- CPU에선 보다 지연시간을 최소화하기 위해 자체 메모리를 갖춘다 (레지스터,캐시)

- 자주사용하는 명령어 일 수록 코어와 가까이 배치

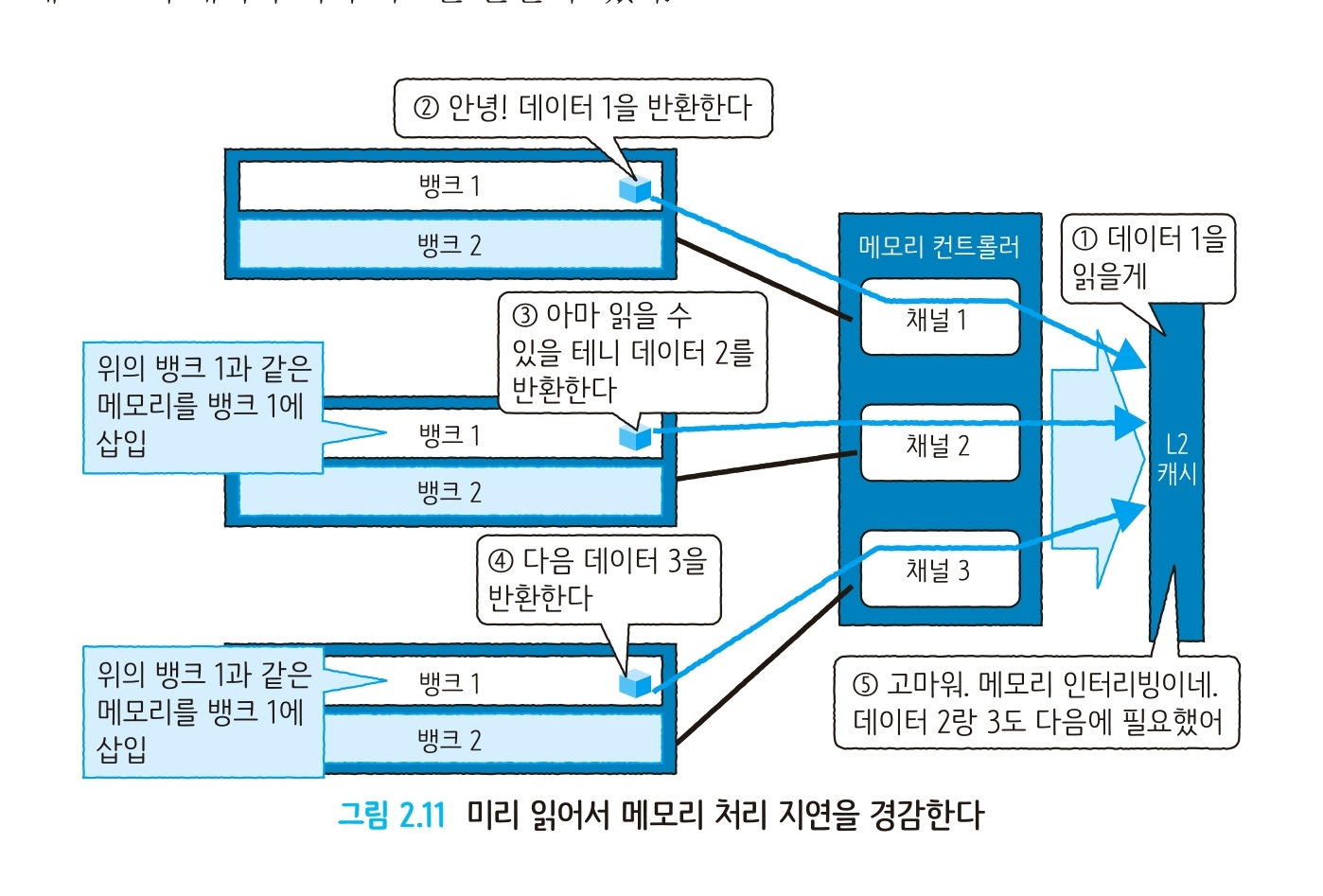

- 메모리 인터리빙 : 미리데이터를 메모리가 CPU에 전달하여 처리시간 최소화

- 메모리컨트롤러와 채널을 통해 메모리 CPU 간 데이터 통신

- 데이터는 대부분 연속해서 엑세스되기 때문에 연속되는 데이터를 미리 다보내서 지연시간 최소화

- 뱅크를기반으로 연속되는 데이터를 배치하기 때문에 규칙을 지켜야한다..

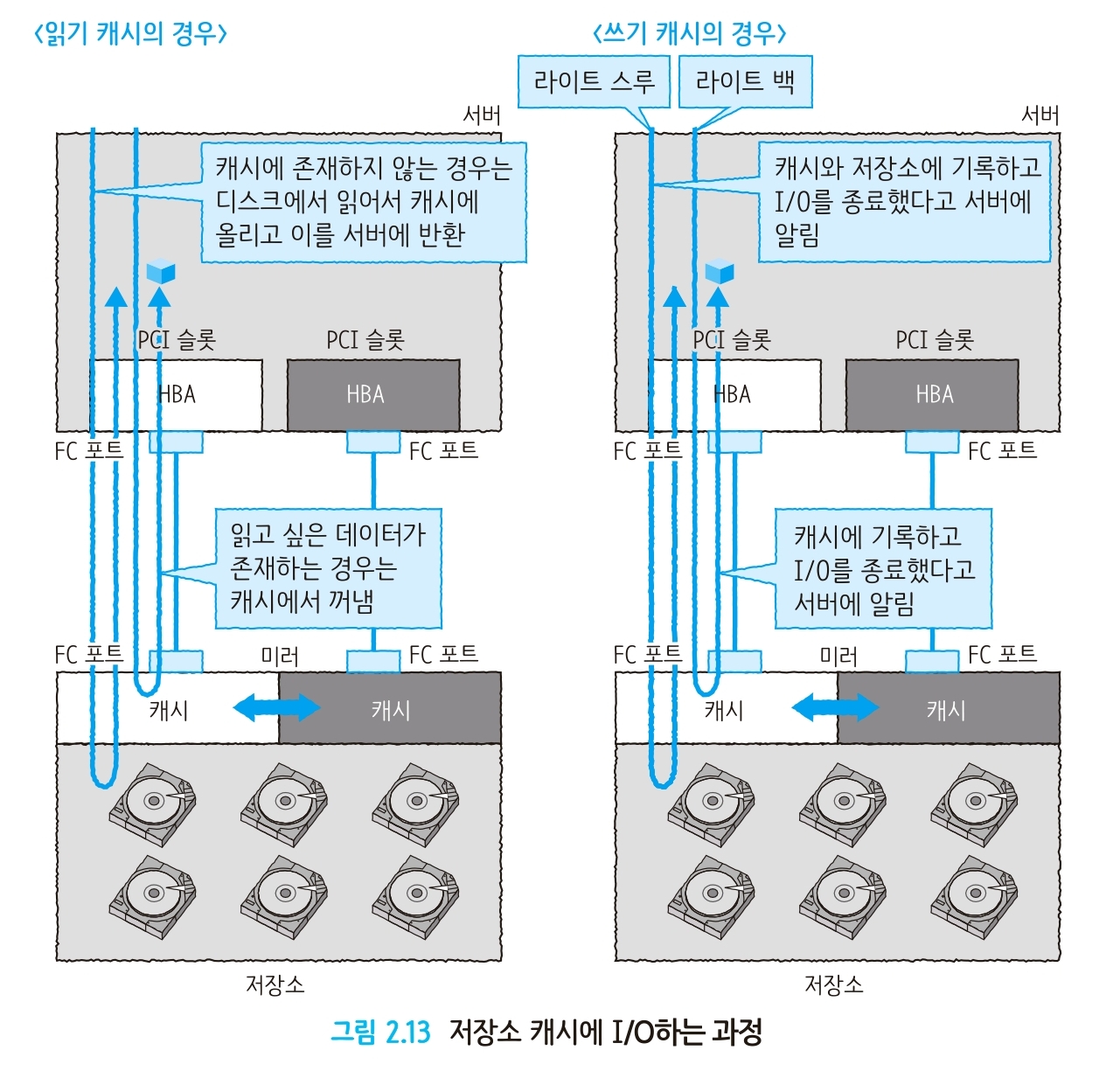

3. 저장장치 쓰기/ 읽기

- 서버마다 별도로 디스크를 가지기도 하지만, 별도의 저장소(SAN) 을 구성하기도한다.

- 일반적으로 SAN과 연결시 FC 광채널을 이용

- 이러한 광채널에 접속하기 위해서는 FC포트가 요구 ⇒ PCI 슬롯에 HBA 삽입

- 데이터 읽기: 캐시에 데이터 있을 경우, 캐시로부터 데이터 획득 / 없는경우, 저장소로 접근

- 데이터쓰기

- 1) Write back: 캐시에 데이터쓰고 쓰기종료 / 캐시를 별도로 미러링 ⇒ 안정성 향상

- 2)Write through: 캐시와데이터 모두 쓰기 발생 ⇒ 확실하지만 캐시의 장점이 없다.

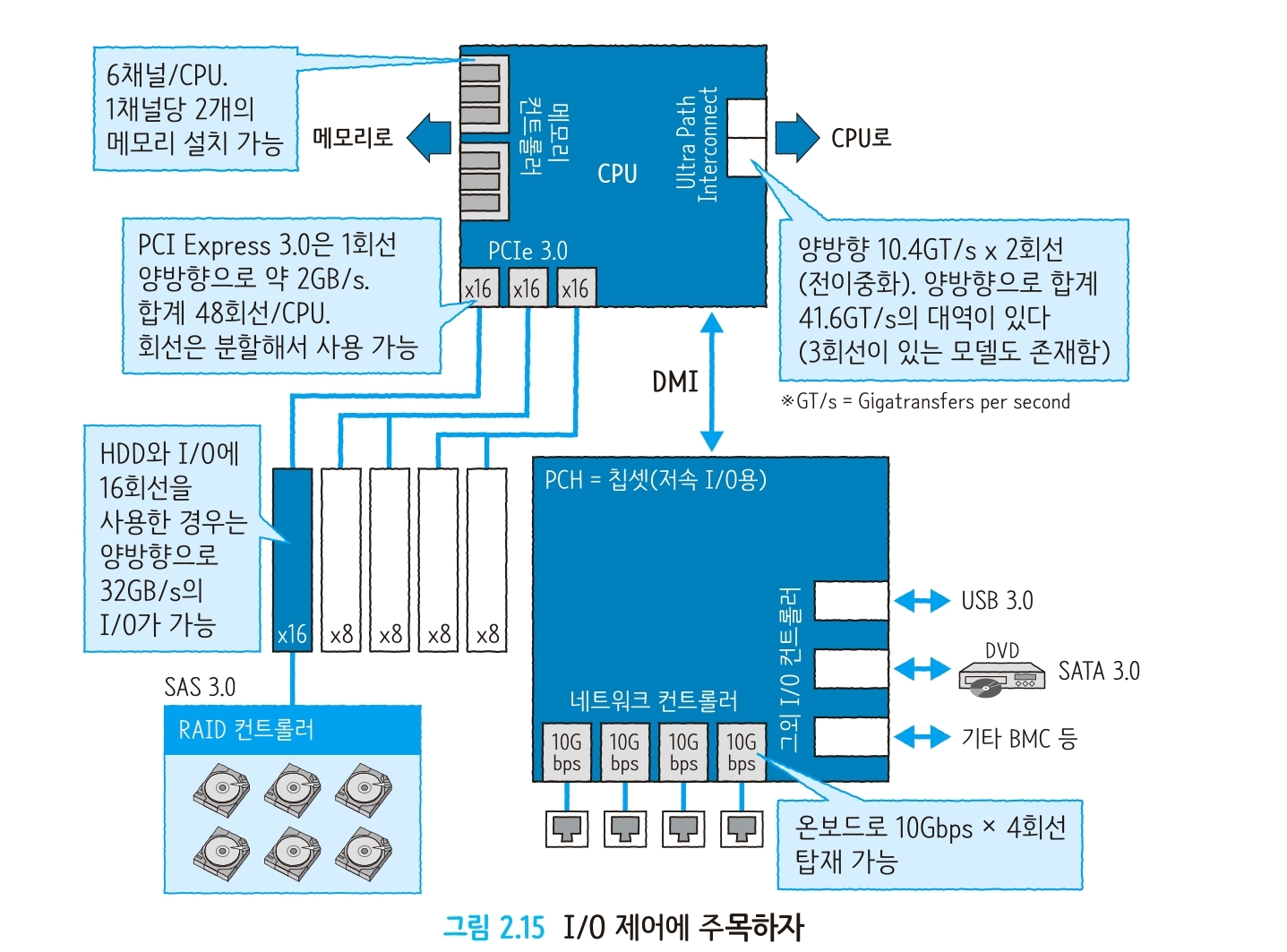

4. 입출력 제어

- PCH: Platform Controller Hub , CPU제어 메모리나 PCIe 외의 입출력 속도가 느린 입출력 장치서 사용

1) PCI x8, x16

- 회선 숫자를 의미

- 위 사진의 CPU의경우 48개 회선이 있다. 그리고 본인의 설정에 따라 회선을 나누어 사용

- 양방향으로 회선당 2GB/s 이면 x16 에선 2 x 16 = 32GB

- PCI컨트롤러: 병목지점 방지 , CPU를 통한 직접제어

⇒CPU와 칩셋의 구별:다양한컨트롤러를 CPU와 먼곳 , 입출력장치 주변에 배치하여 CPU는 연산에집중, 입출력 효율화

5. 데이터 전송

1)대역

- 한번에 데이터를 보낼 수 있는 데이터폭 (전송폭) X 1초에 전송할 수 있는 횟수 (전송횟수)

답글 남기기